-

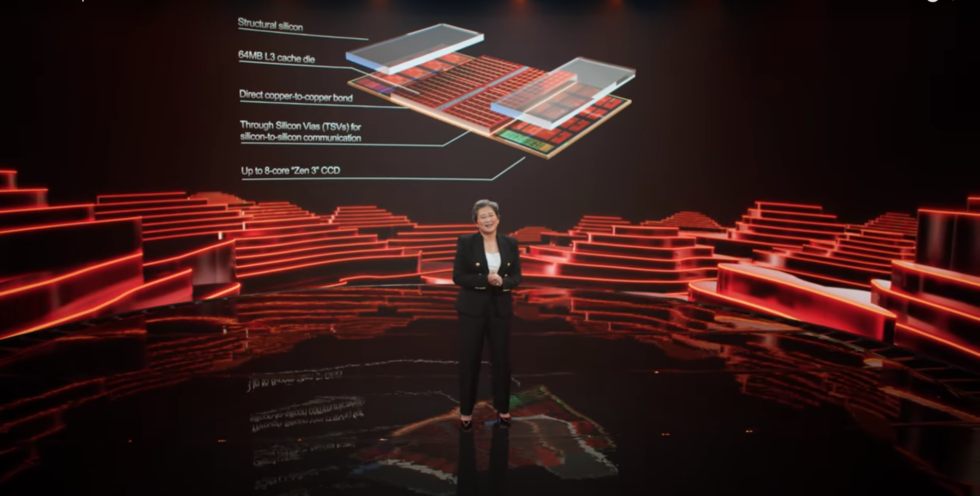

This exploded diagram shows an additional 64MiB of L3 cache atop the center of the CCD, with structural silicon inserts to either side of the new layer. [credit: AMD ]

Yesterday at Computex 2021, AMD CEO Lisa Su showed off the company's next big performance play—3D stacked chiplets, allowing the company to triple the amount of L3 cache on its flagship Zen 3 CPUs.

The technology is just what it sounds like—a layer of SRAM cache sitting atop the Complex Core Die (CCD) of the CPU itself. Current Zen 3 architecture integrates 32MiB of L3 cache per eight-core chiplet—making 64MiB total for a 12- or 16-core chiplet like the Ryzen 9 5900X or 5950X. The new technology adds an additional 64MiB L3 cache on top of each chiplet's CCD, bonded with through-silicon vias (TSVs).

The additional 64MiB L3 cache layer does not extend the width of the CCD, resulting in a need for structural silicon to balance pressure from the CPU cooling system. Compute and cache dies are both thinned in the new design, allowing it to share substrate and heat spreader technology with current Ryzen 5000 processors.

No comments:

Post a Comment